sem-VIII (CBSGS) ETRX - C'MOS 121 5

Q.P. Code: 719702

(3 Hours)

[Total Marks: 80

www.a2zsµbjects.com

5

www.a2zsubjects.com

5

www.a2zsubjects.com N.B.:(1)Question ONE is compulsory.

- Solve any THREE out of remaining questions. (2)

- Draw neat and clean diagrams. (3)

- Assume suitable data if required. (4)

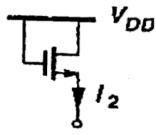

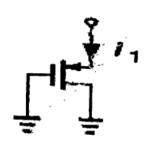

- (a) Will the following circuits work as current sources? Give the correct reason for your answer.

- (b) List down the performance parameters of VCO and explain trade off between them.

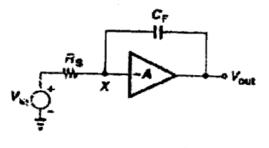

- (c) Calculate the pole associated with the node X shown in the following figure. Assume  $R_s = 1K\Omega$ ,  $C_F = 0.1pF$  and A = 10.

- (d) Draw and explain the floor plan for a possible mixed signal chip.

- (a) Show the op-amp based implementation of temperature independent 10 bandgap reference and various issues involved thereof.

- (b) For common source stage with diode connected load, if the variation of  $\eta = (g_{mb}/g_m)$  with the output voltage is neglected then prove that the gain is independent of bias currents and voltages.

TURN OVER

www.a2zsubjects.com

www.a2zsubjects.com

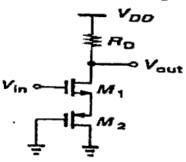

(c) Assuming  $\lambda = \gamma = 0$ , calculate the small signal gain of the circuit shown:

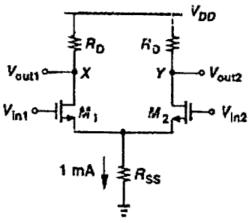

- (a) The following circuit shown in Figure uses a resistor rather than a current source to define a tail current of 1mA. Assume  $(W/L)_{1,2} = 25/0.5$ ,  $\mu_a C_{ox} = 50 \ \mu A/V^2$ ,  $V_{TH} = 0.6 \ V$ ,  $\lambda = \gamma = 0 \ and \ V_{DD} = 3 \ V$ .

- (a) What is the required input CM for which Rss sustains 0.5V?

- (b) Calculate R<sub>D</sub> for a differential gain of 5.

- (b) Explain the concept of switched capacitor circuit. Draw and explain discrete time integrator along with the output waveform.

- (a) With the use of small signal behaviour, prove that for differential pair the magnitude of differential gain is equal to  $g_m R_D$  regardless of how the inputs are applied.

- (b) What is the need of compensating operational amplifiers? Explain the compensation of two stage operational amplifiers?

- (c) Derive an expression for the input referred noise voltage of common source stage.

TURN OVER

www.a2zsubjects.com

www.a2zsubjects.com

5

5

www.a2zsubjects.com

www.a2zsubjects.com

www.a2zsubjects.com

2

3

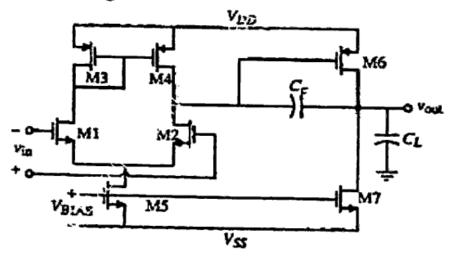

(a) Design two stage Operational Transconductance Amplifier (OTA) similar to that shown in the figure to meet the following specifications with a phase margin of 60°:

| $A_v >$ | 5000 | V | / | V |

|---------|------|---|---|---|

|---------|------|---|---|---|

$$V_{DD} = 2.5 \text{ V}$$

$$V_{ss} = -2.5 \text{ y}$$

Gain Bandwidth (GB) =

$$10MHz$$

$$C_L = 10pF$$

$$V_{out}$$

range =  $\pm 2.5 \text{ V}$

Slew Rate (SR) > 10 V/

$$\mu$$

s ICMR = -1 to 2 V

$$P_{diss} \le 2 \text{ mW}$$

Use the following table for material and device parameters. Assume  $C_{ox} = 2.47 \text{ fF/}\mu\text{m}^2$ .

| Parameter | n - channel    | p - channel     | Unit  |

|-----------|----------------|-----------------|-------|

| $V_{TO}$  | $0.7 \pm 0.15$ | $-0.7 \pm 0.15$ | V     |

| K'        | 110            | 50              | μΑ/V² |

| λ         | 0.04           | 0.05            | V-1   |

Verify that the voltage gain and power dissipation given in the specifications are met by the designed circuit.

- (b) Explain charge-pump PLL.

- 6. (a) Compare the performance of various op-amp topologies.

- (b) Explain the input-output characteristics of phase detector (PD) circuit.

- (c) Explain the concept of clock feedthrough.

- (d) Compare between full-custom and semi-custom design.

www.a2zsubjects.com

www.a2zsubjects.com

www.a2zsubjects@omp 5

5

5